Courses

Comprehensive skill-building courses providing just-in-time and on-demand learning

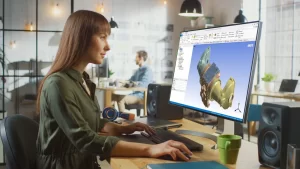

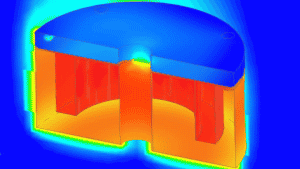

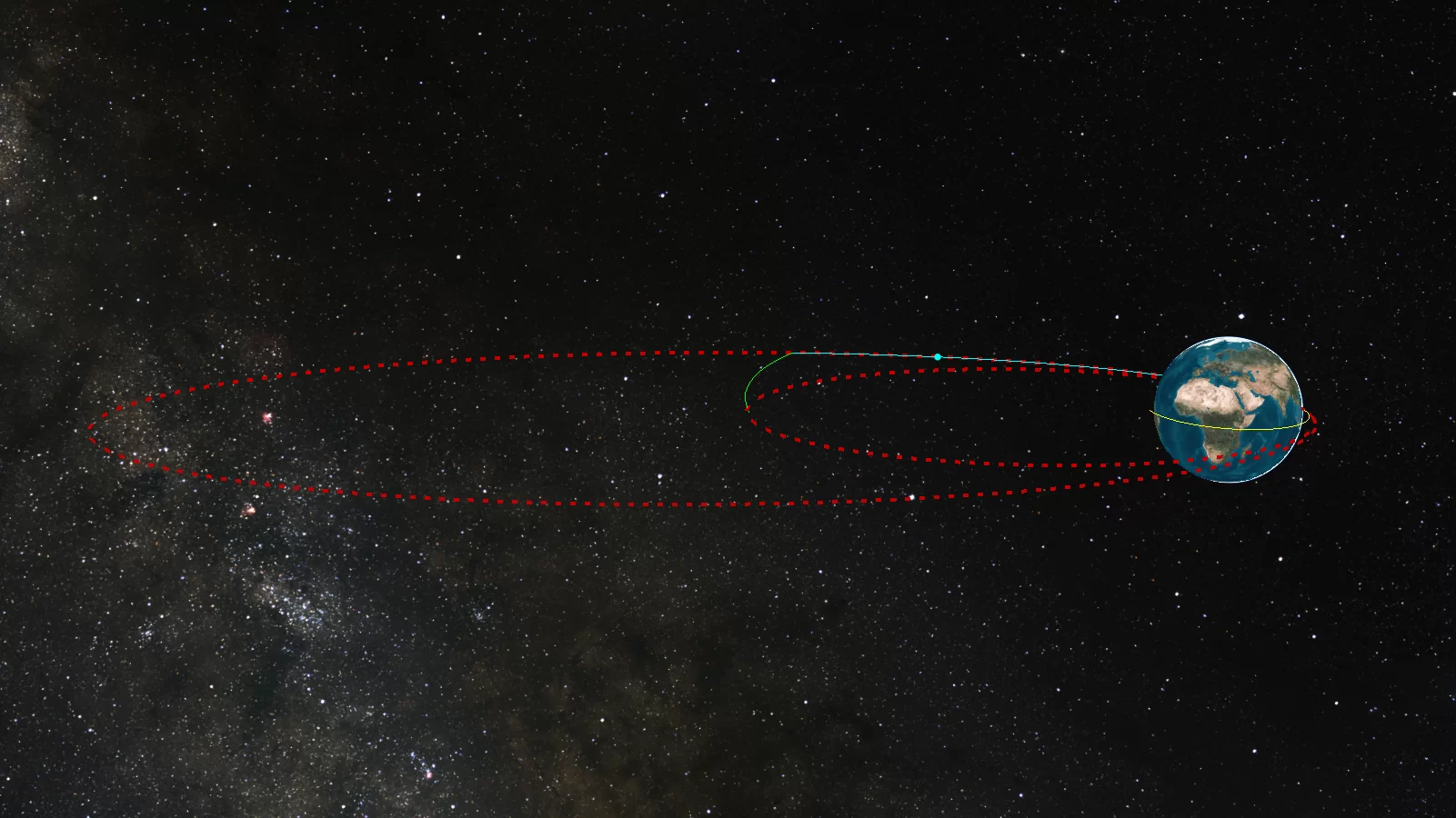

Watch

Watch engaging online video lectures from subject matter experts

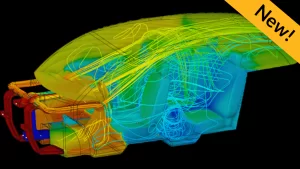

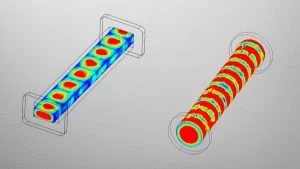

Practice

Solve practical hands-on examples using Ansys software

Assess

Test your retention using quizzes and homework